### **BAB IV**

### HASIL DAN PEMBAHASAN

### 4.1 Pendahuluan

Bab ini membahas hasil pengujian yang dilakukan di laboratorium. Penelitian ini mencakup hasil kontrol kecepatan *SRM* berbasis *PWM* dengan beberapa kondisi percobaan. Pengukuran gelombang pada saat pengujian alat dilakukan di setiap rangkaian diantaranya *Cyclone IV FPGA*, *driver* TLP 250, *DC-DC Isolated Regulator*, Asymmetric Converter, *Sensor Arus LEM HX-10P* menggunakan osiloskop digital.

Hasil pengukuran yang akan dibahas pada bab ini adalah bentuk sinyal pengapian *SRM*, yang dipengaruhi oleh sinyal pembawa pada pengaturan sinyal modulasi dan hasil arus tiap fasa pada setiap percobaan serta hasil kecepatan rotor seperti yang diukur oleh takometer. Pengukuran dilakukan sebagai alat bukti otentik atas perangkat keras yang dibuat oleh penulis sesuai dengan teori dan perancangan perangkat keras pada BAB II dan BAB III.

## 4.2 Hasil Pengujian Perangkat Keras

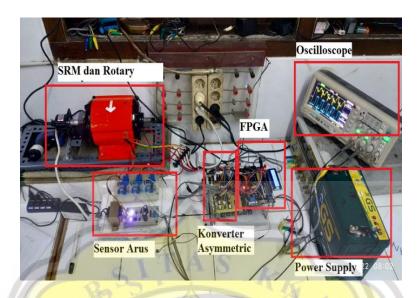

Implementasi perangkat keras sistem kontrol kecepatan *SRM* berbasis *PWM* disajikan pada Gambar-4.1 yang terdiri dari catu daya, rangkaian daya konverter asimetris, pengontrol sinyal digital *FPGA*, *rotary encoder*, rangkaian sensor arus *HX 10-P/SP2* dan osiloskop digital.

Gamb<mark>ar-4. 1 Implementasi perangkat keras sistem kendali kece</mark>patan SRM

Pada pengujian ini, FPGA Cyclone IV digunakan sebagai pengontrol dan rotary encoder sebagai pendeteksi posisi rotor. Pulsa keluaran dari rotary encoder pin A dan pin Z digabungkan untuk menghasilkan pulsa yang merepresentasikan posisi rotor terhadap stator pada kontroler FPGA. Pulsa tersebut akan digunakan sebagai referensi eksitasi, pin pulsa A pada rotary encoder dihubungkan dengan INT 1 sebagai penghitung pulsa interupsi dan pulsa pin Z digunakan sebagai interupsi jika pulsa pin A telah melewati satu putaran penuh. Selanjutnya hasil informasi posisi rotor akan diterima dan diolah dengan FPGA ,sehingga menghasilkan pulsa pensaklaran pada SRM. Pulsa pensaklaran SRM pada kontroller FPGA ditambahkan dengan pengaturan PWM yaitu antara sinyal carrier terhadap sinyal modulasi, sehingga kecepatan putar rotor SRM dapat berubah ubah sesuai nilai sinyal modulasi yang diberikan.

Tabel-4. 1 Parameter alat penelitian SRM

| Parameter   | Nilai | Satuan |

|-------------|-------|--------|

| Stator      | 12    | -      |

| Rotor       | 8     | -      |

| Resistansi  | 4.5   | Ohm    |

| Indukstansi | 1.4   | mH     |

| Tegangan    | 12    | Volt   |

Pengujian dilakukan dengan mengubah nilai sinyal modulasi terhadap sinyal *carrier* 15000 pada sinyal pensaklaran *SRM*, dengan duty cycle 100% nilai sinyal modulasi sebesar 15000, dengan duty cycle 93% nilai sinyal modulasi sebesar 14000, dengan duty cycle 86% nilai sinyal modulasi sebesar 13000. Dengan duty cycle 80% nilai sinyal modulasi sebesar 12000, dengan duty cycle 73% sinyal modulasi diseting sebesar 11000 dan dengan duty cycle 66% sebesar 10000.

# 4.2.1 Hasil Pengujian Alat Percobaan Pertama

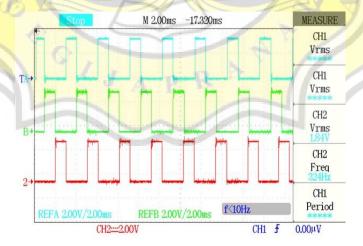

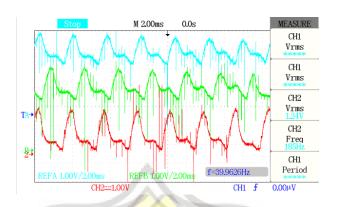

Gambar-4. 2 Hasil gelombang pensaklaran SRM 3 fasa dengan duty cycle 100%

Dari pola pensaklaran yang ditunjukkan pada Gambar-4.2, dalam satu siklus terdapat delapan proses pola pensaklaran berurutan untuk setiap fasenya. Perpindahan tiap fasa bergeser 15° satu sama lain dimulai dari *Phase A, Phase B*, dan *Phase C*, sehingga *SRM* dapat beroperasi secara optimal.

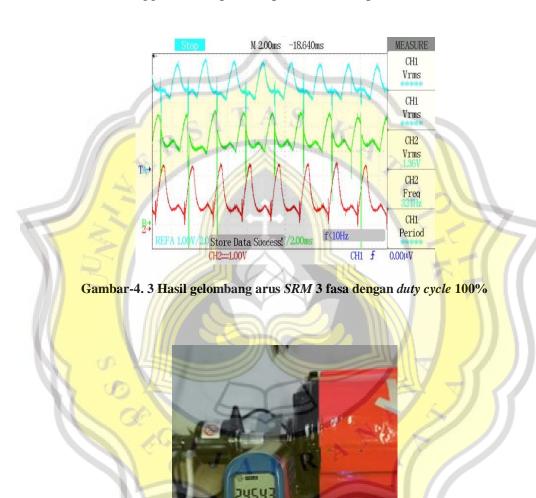

Gambar-4. 4 Hasil kecepatan motor pada duty cycle 100%

Pada Gambar-4.3 arus fasa saat *duty cycle* diatur pada skala 100%, menghasailkan arus yang tinggi dengan kecepatan rotor 2454 RPM. Maka semakin tinggi kecepatan rotor maka semakin besar nilai *back-EMF* maka menandakan hasil keluaran daya optimal.

# 4.2.2 Hasil Pengujiaan Alat Percobaan Kedua

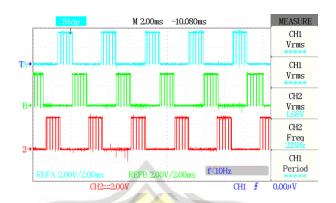

Pengujian alat pada percobaan kedua sinyal modulasi diatur dengan diturunkan menjadi 14000 sehingga kontrol *FPGA* akan mengaktifkan pensaklaran pada jarak *duty cycle* 93%. Pada kondisi sinyal pensaklaran *SRM* ini terkombinasi dengan sinyal *PWM* sehingga menghasilkan pola pensaklaran yang ditunjukkan pada Gambar- 4.5.

Gambar-4. 5 Hasil gelombang arus SRM 3 fasa dengan duty cycle 93%

Hasil pengujian pada *duty cycle* 93% menghasilkan gelombang arus untuk setiap fasa dengan nilai arus puncak sekitar 1,4 Ampere yang ditunjukkan pada Gambar-4.6, dan kecepatan 2210 RPM seperti pada Gambar-4.7. Pada kondisi ini, putaran SRM mengalami penurunan kecepatan sebesar 244 RPM dari kondisi sebelumnya.

Gambar-4. 6 Hasil gelombang arus SRM 3 fasa dengan duty cycle 93%

Gambar-4. 7 Hasil kecepatan motor pada duty cycle 93%

# 4.2.3 Hasil Pengujian Alat Percobaan Ketiga

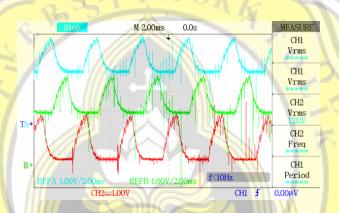

Pengujian alat pada percobaan ketiga sinyal modulasi diatur dengan diturunkan menjadi 13000 sehingga kontrol *FPGA* akan mengaktifkan pensaklaran pada jarak *duty cycle* 86%. Pada kondisi ini sinyal pensaklaran *SRM* terkombinasi dengan sinyal *PWM* sehingga menghasilkan pola pensaklaran yang ditunjukkan pada Gambar- 4.8.

Gambar-4. 8 Hasil gelombang arus SRM 3 fasa dengan duty cycle 86%

Gambar-4. 9 Hasil gelombang arus SRM 3 fasa dengan duty cycle 86%

Hasil pengujian pada *duty cycle* 86% menghasilkan bentuk gelombang arus untuk masing-masing fasa dengan nilai arus puncak sekitar 1,4 Ampere seperti yang ditunjukkan pada Gambar-4.9, dan kecepatan 1682 RPM yang ditunjukkan pada Gambar-4.10. Pada kondisi ini, kecepatan SRM berkurang sebesar 528 RPM dari kondisi sebelumnya.

Gambar-4. 10 Hasil kecepatan motor pada duty cycle 86%

# 4.2.4 Hasil Pengujian Alaat Percobaan Keempaat

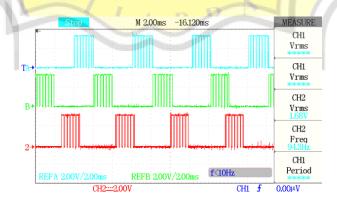

Pengujian alat pada percobaan keempat sinyal modulasi diatur dengan diturunkan menjadi 12000 sehingga kontrol *FPGA* akan mengaktifkan pensaklaran pada jarak *duty cycle* 80%. Pada kondisi ini sinyal pensaklaran *SRM* terkombinasi dengan sinyal *PWM* sehingga menghasilkan pola pensaklaran yang ditunjukkan pada Gambar- 4.11.

Gambar-4. 11 Hasil gelombang arus SRM 3 fasa dengan duty cycle 80%

Gambar-4. 12 Hasil gelombang arus SRM 3 fasa dengan duty cycle 80%

Gambar-4. 13 Hasil kecepatan motor pada duty cycle 80%

Hasil pengujian pada *duty cycle* 80% menghasilkan gelombang arus untuk masing-masing fasa dengan nilai arus puncak sekitar 1,3 Ampere yang ditunjukkan pada Gambar-4.12, dan kecepatan 1501 RPM yang ditunjukkan pada Gambar-4.13. Pada kondisi ini putaran SRM mengalami penurunan kecepatan 181 RPM dari kondisi sebelumnya.

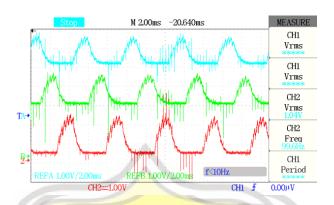

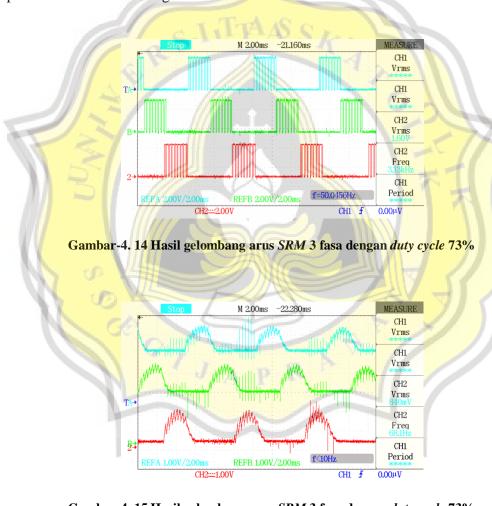

## 4.2.5 Hasil Pengujian Alat Percobaan Kelima

Pengujian alat pada percobaan kelima sinyal modulasi diatur dengan diturunkan menjadi 11000 sehingga kontrol *FPGA* akan mengaktifkan pensaklaran pada jarak *duty cycle* 73%. Pada kondisi ini sinyal pensaklaran *SRM* terkombinasi dengan sinyal *PWM* sehingga pola pensaklaran yang ditunjukkan pada Gambar- 4.14 sebagai berikut.

Gambar-4. 15 Hasil gelombang arus SRM 3 fasa dengan duty cycle 73%

Hasil pengujian pada *duty cycle* 73% menghasilkan bentuk gelombang arus untuk masing-masing fasa dengan nilai arus puncak sekitar 1,2 Ampere

seperti terlihat pada Gambar-4.14, dan kecepatan 1501 RPM seperti pada Gambar-4.15. Pada kondisi ini putaran SRM mengalami penurunan kecepatan 181 RPM dari kondisi sebelumnya.

Gambar-4. 16 Hasil kecepatan motor pada duty cycle 73%

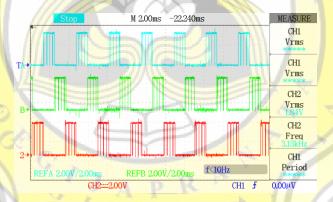

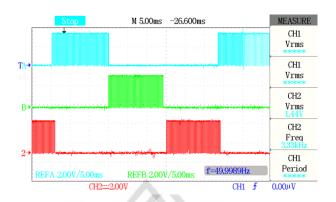

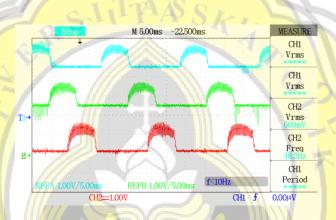

# 4.2.6 Hasil Pengujian Alaat Percobaan Kenam

Pengujian alat pada percobaan terakhir sinyal modulasi diatur dengan diturunkan menjadi 10000 sehingga kontrol *FPGA* akan mengaktifkan pensaklaran pada jarak *duty cycle* 66%. Pada kondisi ini sinyal pensaklaran *SRM* terkombinasi bersama sinyal *PWM* sehingga pola pensaklaran menjadi seperti yang ditunjukkan pada Gambar- 4.17.

Gambar-4. 17 Hasil gelombang arus SRM 3 fasa dengan duty cycle 66%

Gambar-4. 18 Hasil gelombang arus SRM 3 fasa dengan duty cycle 66%

Gambar-4. 19 Hasil kecepatan motor pada duty cycle 66%

Pada duty cycle 66% kecepatan putar awal 1053 RPM mengalami perlambatan hingga 690 RPM. Percobaan ini mengalami penurunan kecepatan yang sangat tinggi dengan selisih 363 RPM. Gambar-4.18. menunjukkan arus fase menurun. Gambar-4.19 memperlihatkan kecepatan putar awal rotor sebesar 690 RPM. Hal ini dibuktikan dengan nilai arus puncak yang lebih kecil yaitu 1 Ampere dibandingkan arus rata-rata sehingga kecepatan motor lebih lambat karena sumber tegangan input ke *SRM* dibatasi oleh kontrol *PWM* oleh *FPGA*. Untuk memperjelas hasil percobaan perangkat keras *SRM*, perubahan kecepatan dalam fase pengujian disajikan pada Tabel-4.2.

Tabel-4. 2 Hasil perubahan kecepatan

| Duty Cycle | Nilai Arus | Kecepatan putar(RPM) |  |

|------------|------------|----------------------|--|

| 100 %      | 1,4 A      | 2454 RPM             |  |

| 93 %       | 1,4 A      | 2210 RPM             |  |

| 86 %       | 1,3 A      | 1682 RPM             |  |

| 80 %       | 1,2 A      | 1501 RPM             |  |

| 73 %       | 1,2 A      | 1053 RPM             |  |

| 66 %       | 1 A        | 610 RPM              |  |

#### 4.3 Pembahasan

Switched reluctance motor (SRM) menjadi kandidat kuat untuk transportasi elektrik karena strukturnya yang sederhana, kokoh, biaya rendah, kemampuan toleransi kesalahan kecil, dan keandalan tinggi. Aplikasi untuk kendaraan listrik hybrid (HEVs) atau kendaraan listrik (EVs) membutuhkan kemampuan pengembangan torka tinggi. Dalam penelitian ini pengendalian kecepatan kinerja SRM bertujuan untuk memaksimalkan efisiensi kinerja SRM untuk transportasi listrik dengan memberikan pengaturan PWM. Dengan

memberikan kontrol kecepatan berbasis PWM dapat menghasilkan torsi yang bervariasi pada SRM. FPGA Altera Cyclone IV dapat mengontrol kecepatan SRM dengan respons yang cepat dan tepat. SRM dengan spesifikasi delapan buah rotor dan dua belas buah stator tiga fasa diuji dengan tegangan DC 12 Volt. Kontrol kecepatan SRM dalam kontrol FPGA dilakukan dengan mengubah sinyal modulasi dari sinyal pembawa yang telah diatur dalam program HDL verilog. Sinyal tersebut dikendalikan oleh FPGA yang di dalamnya terdapat penggabungan program clock, counter, D-FF dan comparator menghasilkan *PWM* yang dipengaruhi oleh perubahan variabel duty cycle. *PWM* yang dip<mark>engaruhi ole</mark>h perubahan variabel *duty cycle* akan diinjeksikan ke dalam pola pergantian switching yang berasal dari konversi sensor rotary encoder yang digunakan sebagai acuan oleh FPGA untuk mengontrol saklar pada konverter asimetris untuk memutar kecepatan SRM. Sinyal keluaran FPGA berupa pola pergantian switching yang diinjeksi PWM yang dipengaruhi oleh perubahan variabel duty cycle akan terlihat pada hasil osiloskop. Gambar-4.5 ditunjukan hasil sinyal pensaklaran dari kontrol FPGA yang sudah terinjeksi kendali kecepatan PWM, sehingga kecepatan akan menurun dari 2454 RPM menjadi 2210 RPM. Gambar-4.8 adalah proses pensaklaran pada dengan duty cycle 86% yang mengasilkan arus dan kecepatan yang lebih kecil dibandingkan dengan percobaan sebelumnya, hal ini karena pengaruh kendali kecepatan PWM pada kontrol FPGA. Untuk melihat hasil keseluruhan percobaan sebagai referensi perbandingan pembaca dapat melihat Tabel-4.1.